一、纳米制程瓶颈催生技术变革

随着半导体工艺逼近1nm物理极限,传统制程升级面临三大挑战:

1. 量子隧穿效应导致漏电率飙升

2. 光刻技术瓶颈使EUV光刻机成本突破1.5亿美元/台

3. 研发成本指数增长:3nm芯片设计成本超5亿美元

台积电数据显示,5nm后工艺节点性能提升幅度从40%骤降至15%,而成本涨幅超30%,摩尔定律的经济效益正在消失。

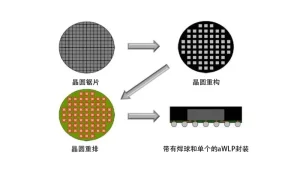

二、Chiplet技术的破局优势

1. 性能突破:

– AMD EPYC处理器采用7nm Chiplet设计,实现128核集成,性能提升140%

– 通过硅中介层实现2.5D/3D堆叠,互连密度达10^6/mm²

2. 成本优化:

– 复用成熟制程芯片(如22nm I/O芯片+5nm计算芯片)降低30%生产成本

– 良率提升法则:单个Chiplet缺陷率从全芯片的15%降至3%

3. 异构集成:

– 英特尔Ponte Vecchio GPU整合47个Chiplet,包含5种制程节点

– 实现存储、计算、射频等不同工艺模块的最佳组合

三、技术挑战与产业格局

核心壁垒:

– 超高密度互连(UCIe标准要求0.5μm间距)

– 热力学管理(3D堆叠热流密度达500W/cm²)

– 测试技术(已知良好芯片KGD筛选)

国际竞争态势:

– 美国(Intel/AMD):掌握EMIB、Foveros等先进封装技术

– 中国台湾(台积电):CoWoS封装产能2023年增长200%

– 中国大陆:封装测试产业占比全球25%,但高端占比不足5%

四、华芯邦的破局之路

1. 技术突破:

– 开发TGV(玻璃通孔)中介层技术,实现8层3D堆叠

– 自主UCIe PHY IP,传输速率达16GT/s

– 热压键合精度控制在±0.25μm

2. 产业布局:

– 与中芯国际共建2.5D封装产线,规划月产能3000片

– 开发国产EDA工具链,支持Chiplet协同设计

3. 战略意义:

– 突破台积电CoWoS技术垄断(市占率92%)

– 构建从设计到封测的完整Chiplet生态

– 在HPC/AI芯片领域实现国产替代(良率已达85%)

五、未来展望

据Yole预测,2027年Chiplet市场规模将达570亿美元,年复合增长率31%。随着中国在先进封装领域投入超千亿资金,华芯邦等企业有望在:

– 光子互连封装

– 芯粒标准化

– Chiplet IP交易平台

等方向实现弯道超车,重塑全球半导体产业格局。