从“芯”到“系统”的范式转移

在半导体行业过去的五十年里,我们习惯于遵循一条简单粗暴的法则:更小的晶体管,更强的性能。这就是著名的摩尔定律。

然而,进入2026年,随着物理极限的逼近,单纯靠微缩晶体管尺寸带来的性价比提升已难以为继。业界普遍的共识是:我们正在从“在芯片上设计系统”转向“在系统里封装芯片”。

先进封装已不再是生产线末端的“打包”环节,而是成为了整个半导体产业的核心竞争力。本文将深入解读当前最新的芯片封装动态,剖析从CoWoS的物理极限到玻璃基板、面板级封装及光电合一的四大技术路线,探讨“封装即系统”时代的架构逻辑。

一、现状审视:为什么封装突然变得“不可或缺”?

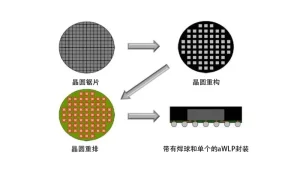

将时间回拨到几年前,封装工程师的工作相对纯粹:把切好的晶圆(Die)粘到基板上,打上金线,灌封胶水,测试通过即可。但在2026年的今天,封装成为了系统性能的“命门”。

这一转变的源动力来自人工智能的爆发。当我们试图构建一个能够处理大语言模型的AI加速器时,单颗芯片的面积已经逼近光刻机的极限,良率也在悬崖式下跌。为了解决这个问题,设计师们将巨大的SoC拆解成若干个小芯粒,再通过先进封装将它们“拼接”在一起。

在这个异构集成的时代,芯粒与芯粒之间的互联速度、功耗以及数据传输密度,完全取决于封装技术。一枚AI芯片的性能,现在不仅仅看代工厂的制程工艺,更要看封测厂的“搭积木”能力。2026年的数据中心旗舰芯片,几乎无一例外地走向了多裸片系统的设计范式。

二、路线解析:四大前沿技术的竞合博弈

目前的先进封装领域不再是单一技术的独角戏,而是呈现出多条技术路线并行发展、分别落地的态势。主要可以分为四大阵营:持续进化的CoWoS、降本增效的CoPoS、颠覆材料的玻璃基板以及面向未来的光电合封装。

1. 旗舰之选:CoWoS 的极限扩张

如果你关注过去几年的高性能计算,CoWoS一定不陌生。它通过一个微小的硅中介层,将计算芯片和HBM高带宽内存连接起来,是目前旗舰AI加速器的标配。

在2026年的最新规划中,CoWoS正试图突破其物理桎梏。传统的CoWoS受限于光刻机的曝光视场,中介层尺寸有限。虽然是最成熟、风险最低的方案,但其天花板清晰可见。随着单一封装内需要集成的HBM堆栈越来越多,硅中介层的面积需求急剧膨胀,从晶圆上切割矩形区域的面积利用率损失较大,这让工程师们不得不寻找替代方案。

2. 新贵登场:CoPoS 与 面板级封装

为了解决CoWoS的面积浪费和高成本问题,CoPoS应运而生。它的核心思想简单直接:既然芯片是方的,为什么非要在圆形的晶圆上做封装?

CoPoS引入了矩形面板。无论是510x515mm还是更大的尺寸,面板级封装能在一张板上排列更多的芯片,材料利用率从晶圆级的不足70%跃升至90%以上。

从技术指标看,目前面板级再分布层的线宽间距已可实现3-5微米,对于连接HBM和逻辑核心已足够。虽然它的规模化量产时间表预计在本十年中后期,但业界已经开始着手解决这一过程中的物理难题。例如,为了攻克玻璃基板在化学气相沉积中的附着力和深孔填充问题,相关设备商正在开发新的电子束量测和CVD技术,以确保在10:1高深宽比的玻璃通孔填充中不产生裂缝。这为CoPoS的量产扫清了关键障碍。

3. 材料革命:玻璃基板的加减法

如果说CoPoS改变了基板的形状,那么玻璃基板则改变了基板的材质。

传统的有机基板在大型封装中容易翘曲,且信号损耗较大。玻璃基板凭借其优异的尺寸稳定性和极低的介电损耗,成为下一代大尺寸、高密度封装的理想基材。

2026年的趋势显示,玻璃基板并非要完全取代传统基板,而是向上攻占最顶端的市场。它允许更精细的布线和更高的互连密度,对于需要传输超高速信号(如SerDes)的芯片具有天然优势。尽管目前玻璃基板的供应链生态远不如有机基板成熟,产线摊销成本较高,但在最顶端、带宽需求最苛刻的系统中(如超大容量交换机芯片),玻璃基板正在成为不可忽视的选项。

4. 终极形态:光电共封装

功耗是算力时代最大的痛点。传统的插拔式光模块在数据中心内耗电惊人。光电共封装技术将光引擎从主板上的可插拔模块,直接移到了芯片封装的内部。

根据2026年的技术路线图,CPO技术即将在2026-2027年间迎来量产拐点。其带来的收益是惊人的:相比传统方案,CPO能提升2倍功耗效率并降低延迟达90%。

这意味着,未来的AI集群互联将不再受限于SerDes的功耗和距离。光信号从芯片边缘直接引出,彻底打破了IO瓶颈。这是封装技术从“电”走向“光”的质变,也是封装即系统最极致的体现。

| 技术路线 | 核心变革 | 关键优势 | 面临瓶颈 |

| CoWoS | 硅中介层 | 技术成熟,风险低 | 面积受限,成本高昂 |

| CoPoS | 矩形面板替代晶圆 | 利用率高,成本大幅降低 | 量产时间未至,设备生态待建 |

| 玻璃基板 | 新材料替代有机基板 | 尺寸稳定,电性能优异 | 供应链不成熟,脆性易裂 |

| 光电共封装 | 光引擎集成至封装内 | 极低延迟,超高能效比 | 产业链整合难度大,散热挑战 |

三、设计生态:从“被动容器”到“主动控制平面”

先进封装的复杂性飙升,带来了一个更深层次的变革:设计方法的改变。

在以往,数字、模拟、封装和PCB设计是相对独立的团队。但在2026年的2.5D/3D AI系统中,封装必须被看作主动控制平面,而非被动的容器。

现实差距是当前业界面临的头号噩梦。理想仿真下的漂亮眼图,在进入封测厂大规模量产时,往往会因为基板的30微米翘曲、焊球的微小塌陷或热漂移而彻底闭合。

为了弥合这一差距,业界正在引入“治理式收敛”的概念。这不再仅仅是设计走线,而是要架构电磁通道。通过对信号完整性、电源完整性和热应力的统一调度,建立从仿真到量产的闭环反馈。

例如,在高性能AI芯粒的电源分配网络设计中,封装内部的本地化电压调节模块必须与裸片谐振点精准匹配。否则,在170-280MHz频段的谐振峰值会击穿目标阻抗,导致系统在高负载下崩溃。这种多维度的物理场协同设计,正在成为封装工程师的必修课。

四、产业博弈:没有赢家通吃,只有分层突围

面对上述如此纷繁复杂的技术选项,半导体公司们该如何押注?答案可能很残酷:大多数人不会“梭哈”一条路。

技术路线图清晰地展示了一个分层级的市场:

1. 旗舰级:在CoPoS等面板方案彻底成熟前,最顶级的AI加速器大概率依然会坚守在CoWoS上,以时间换确定性。

2. 主流级:对成本更敏感的数据中心芯片,将更早地拥抱CoPoS或玻璃基板,享受面积增大带来的成本红利。

3. 边缘与消费级:对价格极度敏感,且对超高速互联需求不那么极致的设备,可能会等待CoWoP路径的成熟——这是一种砍掉传统封装基板,直接贴装到高密度PCB上的激进方案。

对于设计团队而言,应对这种不确定性的策略变得非常现实:接口设计要有封装意识,但不能被单一封装锁定。设计的柔性,是应对封装技术更迭的最低成本手段。

五、封装定义未来

2026年的半导体行业,先进封装已经从一门“手艺”演变为一门“科学”和“艺术”的结合体。

它不再仅仅是关于如何保护一颗芯片,而是关于如何将多颗芯片、光引擎、电源管理单元融合成一个微型的、高性能的系统。无论是CoWoS的极限扩张,CoPoS的几何效率,玻璃基板的材料革新,还是CPO的光电融合,其核心逻辑都是为了解决同一个问题:如何在有限的空间内,塞进更多的计算单元,并养活它们、连接它们。

当摩尔定律的微缩引擎逐渐减速时,先进封装这套复杂的“建筑学”正在为芯片性能的持续增长打开新的物理空间。对于行业观察者和工程师而言,现在是时候将目光从晶圆厂移开,聚焦到封测厂的——因为那里,正发生着比微缩晶体管更激动人心的技术革命。